Semiconductor Wafer Test Conference (SWTest) 2024 Keynote Presentation

## Known Good Die as a Key Enabler for Advanced Packaging in a Disaggregated World

Joe Parks Vice President, Technology Development, Intel Corporation

- Advanced Packaging Trend

- Known Good Die in Disaggregated World

- Singulated Die Sort (SDx) Capability at Intel

- Summary

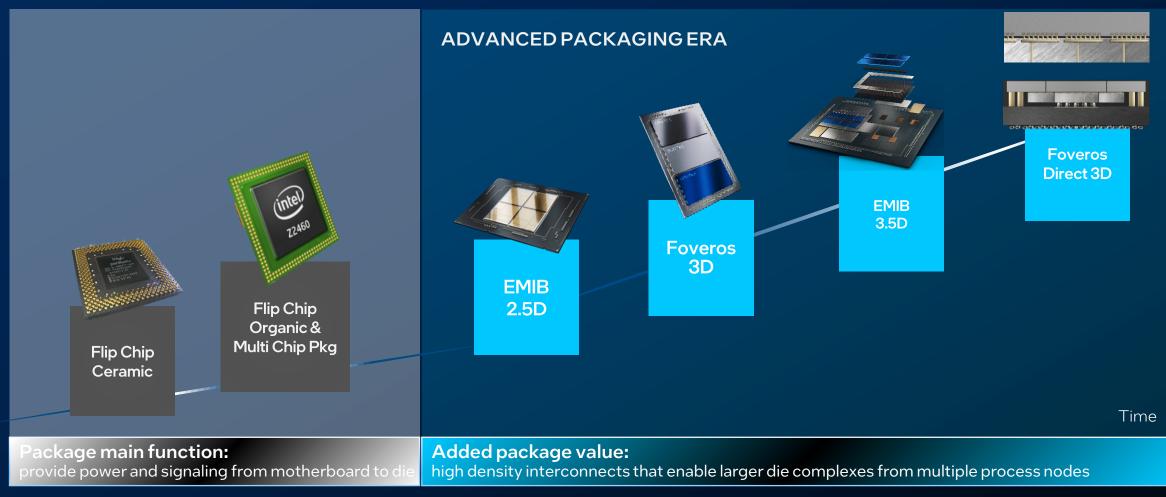

# Intel Package Technology – Expansive Ecosystem

Wafer Level Assembly and Advanced Packaging are an intrinsic part of most compute roadmaps

#### Foundry TD

intel foundry

З

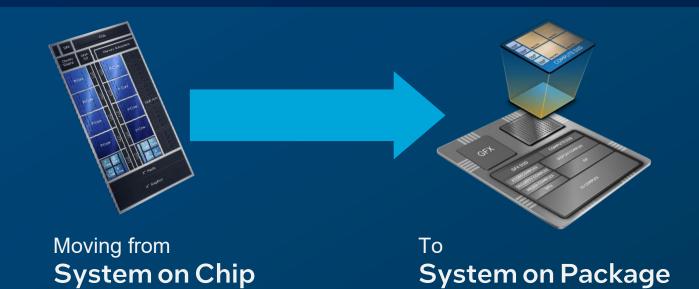

## Disaggregated Flow Advantages

- Flexibility of packaging external and internal IP's to deliver Leadership Products

- Re-use of product design / tiles between products

- Opportunity for improved product yields

- Equivalent or Better Cost Structure vs. Monolithic

#### Modular Manufacturing at work: Intel<sup>®</sup> Data Center GPU Max

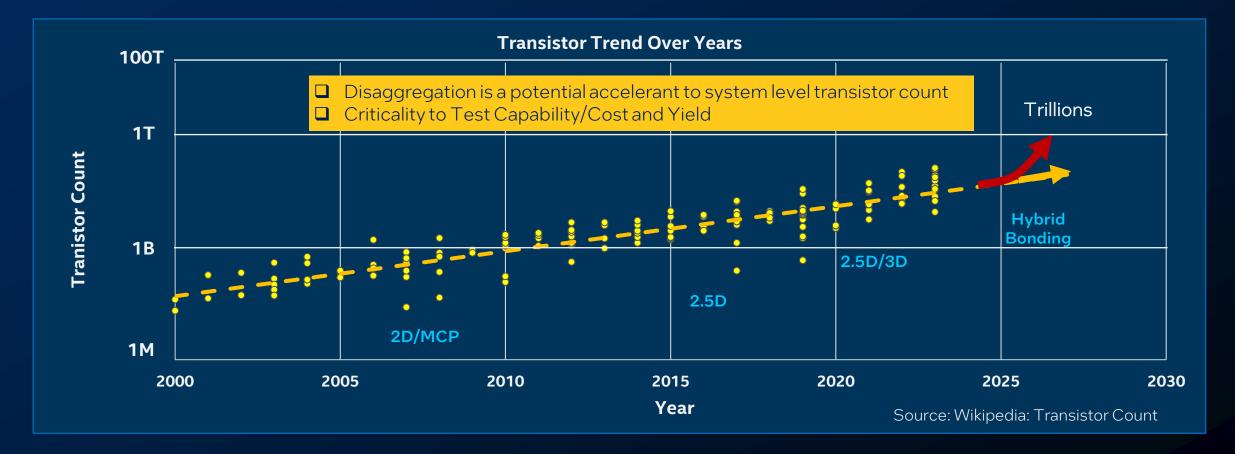

## Transistor Trend: Importance of Test

Trending to hit > 1 Trillion transistors per package by middle of this decade

#### intel foundry

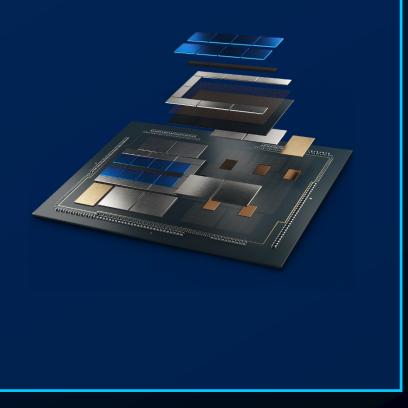

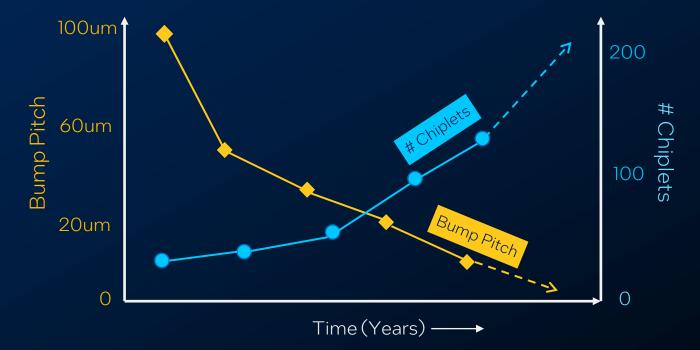

# Challenges in Disaggregation Era

- Bump pitch continues to scale down to <10um with hybrid bonding</li>

- Chiplet count continues to increase

- Plenty of technical challenges to be addressed in the disaggregation world

- Chip to wafer vs wafer to wafer

- 3D stacking, memory integration

- Bump to bump connection: warpage/accuracy

- Chiplet placement & stacking speed

- Testing for interconnect quality/reliability

## What are the possibilities and the challenges as we look into the future?

## Role and Importance of Test in the Advanced Packaging Era

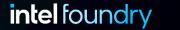

## Typical Test Flow

intel foundry

## Role of Test in Disaggregated World

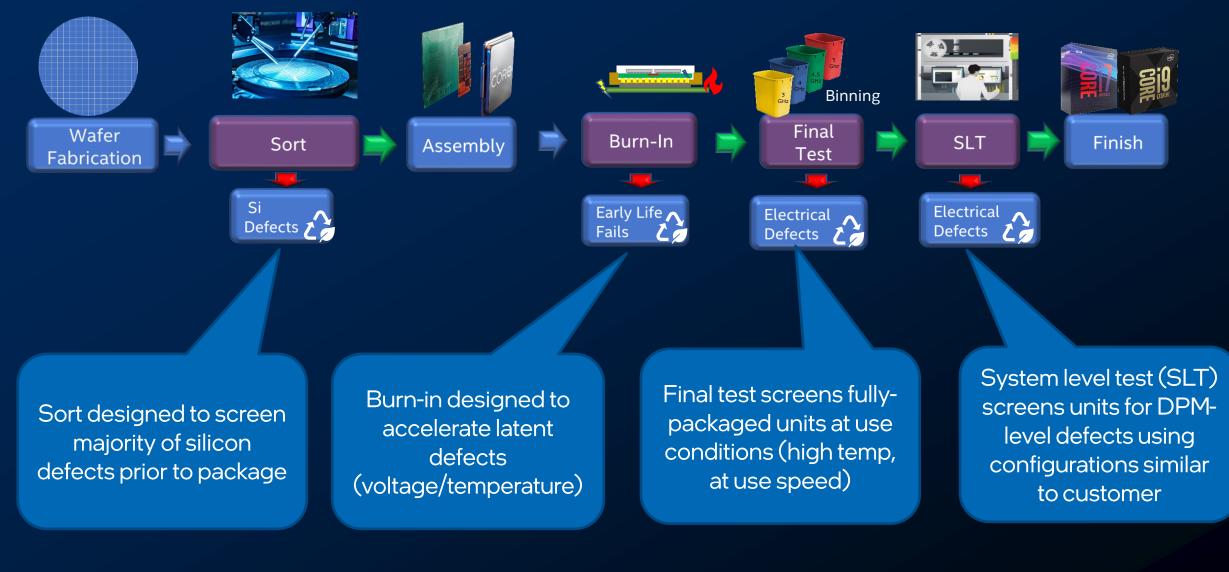

## Easy Example: Single die into a package

9

Yield

**Cost risk**

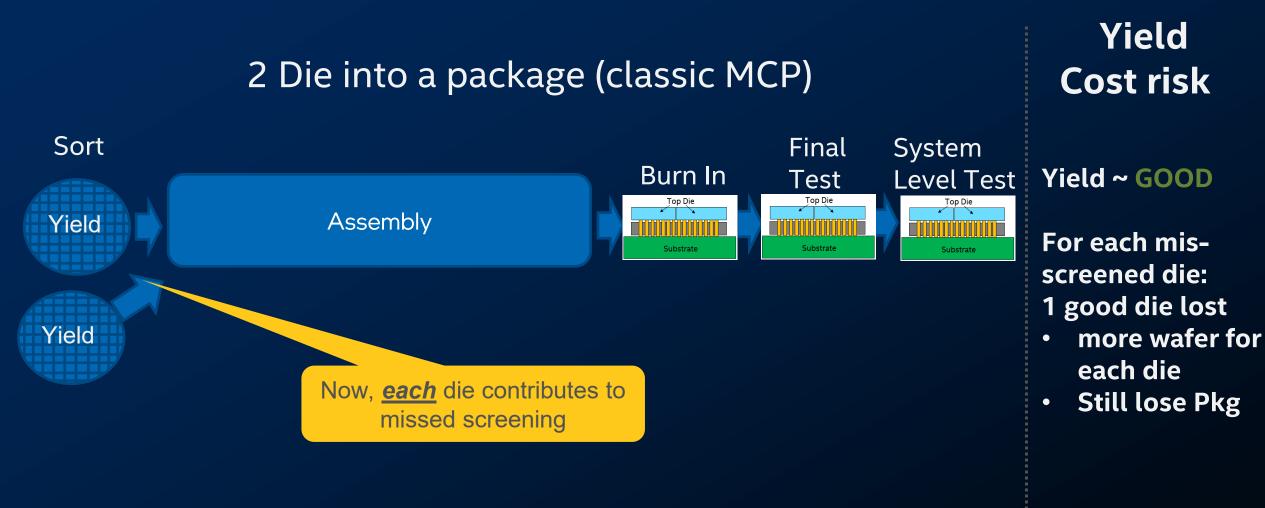

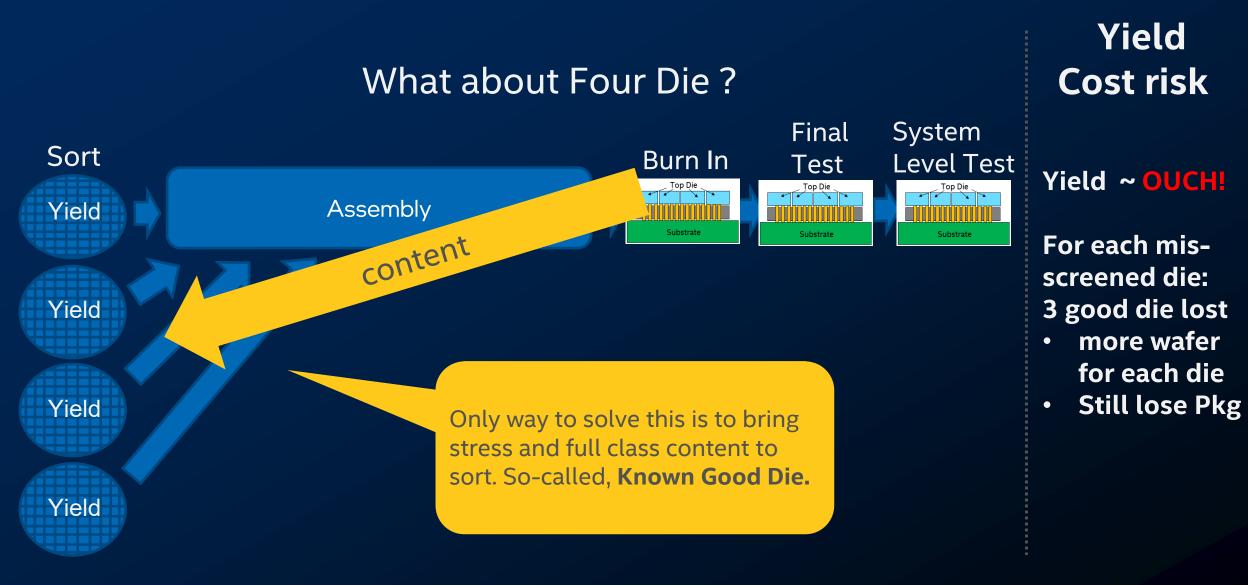

## Role of Test in Disaggregated World

## Role of Test in Disaggregated World

Foundry TD

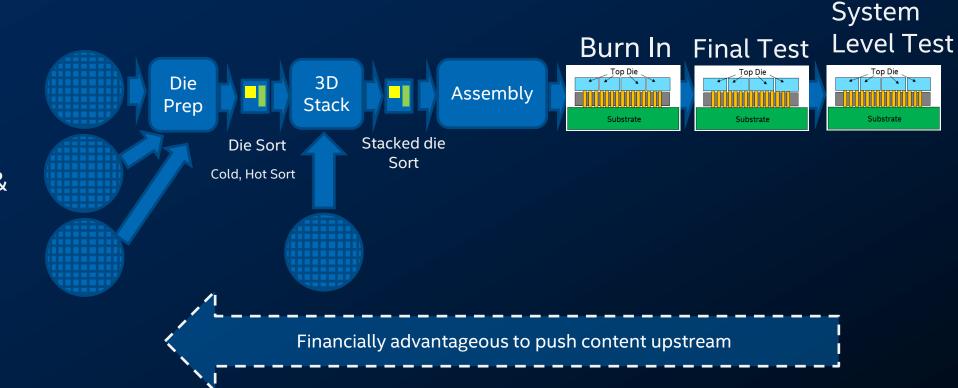

# Beyond classic industry KGD moniker

- "Known Good Die" is testing/screening die prior to assembly & packaging, for all defects and parametric issues in silicon

- KGD is the result of die-level testing under the following conditions

- Total emulation of the final test done on packaged chip, by bringing it at the die-level

- High Thermal stress to catch latent defects

- High Electrical stress (high voltage, frequency) to screen defective die

KGD = Passing Die under stress from all the test conditions

# Intel's Unique Test Method in Disaggregated World

Disaggregated Flow: Multiple die (top & base) stacking & integration into package

Enabling Known Good Die requires a combination of tester platform and thermal control

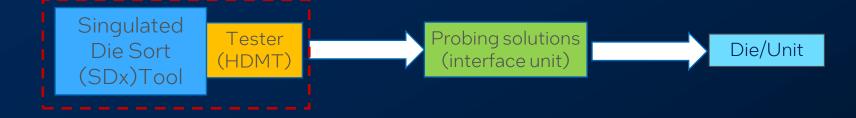

# Intel Solution to enable KGD: Singulated Die Sort

- Singulated Die Sort/Test (SDx) <u>ensures only known-good die</u> survive to wafer level assembly processing

- What is SDx?

- At its core, SDx is a novel thermal system which provides extreme thermal conductivity and response

- Incorporates special die handling capability

- SDx allows full final test (post-package) content and stress test at Sort (pre-package)

- Based on Intel developed HDMT tester (High Density Modular Tester)

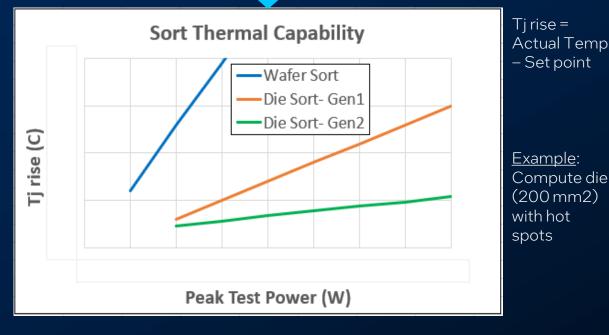

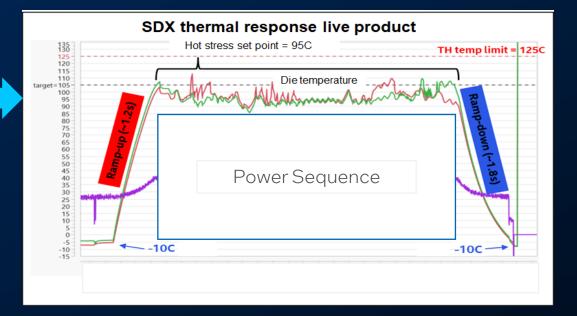

## Die Sort: Intel Thermal Solution

## Best-in-class thermal capability

- 125C temp swing (cold to hot) in 1-2 secs

- >100x more effective thermal capability than wafer sort-based industry solutions

#### SDx enables final test content & stress at Sort

- Captures up to 90% of back-end defects, thus providing higher test yield

- Tests both singulated die and singulated stacked die

- Cold & hot testing merged into a single insertion

## intel foundry

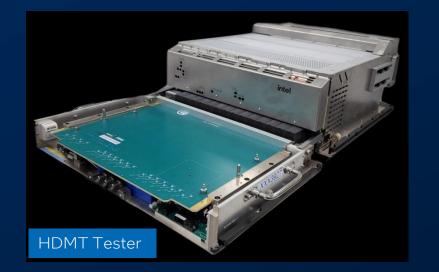

## HDMT: Intel Tester Solution

- High Density Module Tester is another key component of Intel Sort/Test

- Intel designed and manufactured test platform

### Key Advantages/Points:

- Highly re-usable, re-configurable and field upgradable

- Competitive cost-of-test for HVM and Engineering use

- Small footprint: Optimized Modular Architecture

- Integrated Infrastructure

- Modular Design allows multiple generations of capability, with multiple tester configurations tailored to product needs

- Proven tester platform with 12000+ testers running in factories & supporting products

- 1400+ unique test programs; 2000+ users worldwide

## HDMT Capability Overview

## Key Hardware Capability

| Parameter                             | Capability                                                                                                           |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| # Digital IO Channels                 | 896 @1.5 Gpbs<br><b>up to</b> 2240 @ 2 Gpbs                                                                          |  |  |

| # HC/LC DPS Channels                  | 308 total independent resources (HC: 70, LC: 238)<br><b>up to</b> 484 total independent resources (HC: 110, LC: 374) |  |  |

| Vector Memory (per pin pattern depth) | 4GV with 8x channel linking <b>up to</b> 4GV with bottomless                                                         |  |  |

| Simultaneous power to DUT (W)         | 1.3 kW<br><b>up to</b> 4.3 kW                                                                                        |  |  |

## Key Software Capability

- Highly configurable to allow features per customer's needs

- Highly efficient & easy to use Multi-DUT and IP level parallelism

- Dynamic ganging of DPS rails within test flow

- Excellent Power/Thermal control & monitoring

HDMT is a highly capable tester platform that meets all the product requirements

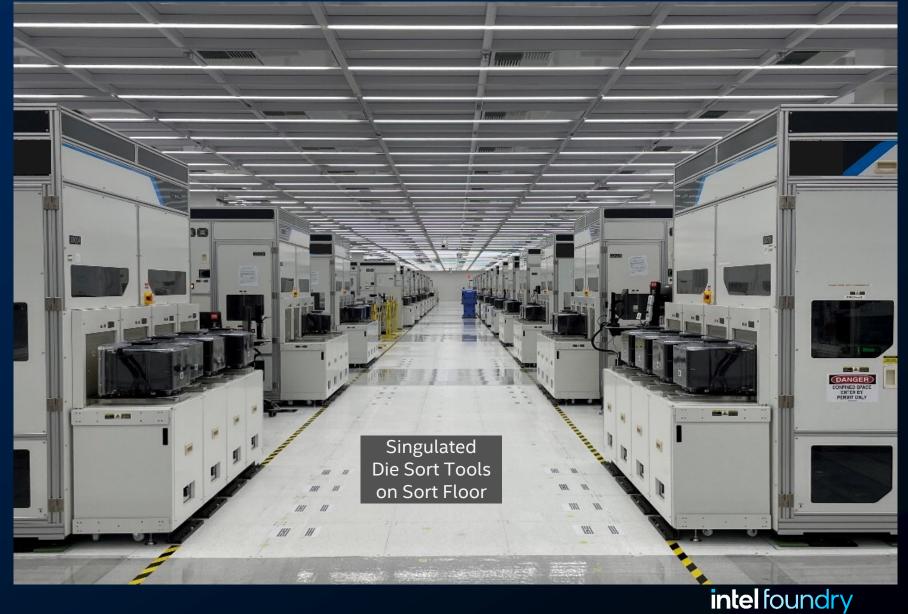

## Intel's Sort Portfolio

HDMT based singulated die sort capability

## Disaggregated Test– Equipment & Tester Capability

Power requirements are trending up for new products, driving the need to deliver higher power during testing of the part

- We must send the needed power and electrical stress for testing new products

- Dynamic Voltage Stress (DVS)

- Voltage Margin Tests

- Time based power sequence

- Active thermal control (beyond thermal head) for test temperature is a key requirement

- Controlled loop for heating and cooling due to thermal control algorithm

- Temperature streaming and multi-modal temperature monitoring using RTD, analog thermal diode and DTS

## Disaggregated Test - Probing Capability

• Power delivery to unit is critical. Small chiplets will have limitations in number of bumps and PDN

Probing solution cannot compromise assembled stack power delivery

| Monolithic Era                                     | Chiplet Era                                                                                              |                                                                  |                                                                                                           |                                 |                                                              |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------|--|

| Sort Probing                                       | Overview                                                                                                 | Sort Probing Solutions                                           |                                                                                                           |                                 |                                                              |  |

| Standard (Monolithic)                              | Mixed bump (large + micro bump)                                                                          | Industry Solution<br>(dedicated test pads)                       | Intel Solution (micro-bump cluster probing)                                                               | Finer pitch<br>micro- bump      | Hybrid Bonding                                               |  |

| 100 um 70 um                                       | Large bump                                                                                               |                                                                  | Quad<br>probing<br>Single<br>probing<br>Patent pending<br>(Quad probe)                                    | ??                              | <b>???</b><br>Innovation needed                              |  |

| >100um pitch                                       | Smaller pitches (<100um) for chiplets                                                                    | <100um (bump pitch),<br>>150um probe pitch                       | 36um to 25um                                                                                              | 25um to 10um                    | < 10um                                                       |  |

| Best Sort Power<br>Delivery (100% bump<br>probing) | Innovative probing solutions needed to sort the different chiplets. Mixed pitch.<br>Multiple probe types | Lower Sort Power Delivery<br>(10% to 20% sort<br>dedicated area) | Best Sort Power Delivery (100% bump probing);<br>Max package Power Delivery (max bump packing<br>density) | Native pitch<br>scaling vs RDL? | Inductive Power<br>coupling, no contact<br>solution, others? |  |

# Beyond Wafer/Die Testing

- Intel's HDMT based overall Test Portfolio includes backend test capabilities, that go together with innovative Die Sort capabilities

- All these test solutions meet the critical needs of disaggregated AI/HPC products

- Die level sort enables full final test content with active thermal control

- Reduces fallout at final test, significantly improving BE yield

#### Burn-In

- High-volume high-power burnin capability

- Active thermal control enables lower STRESS time

- Final Test with advanced thermal control capabilities

- Parallelism opportunities for additional cost savings

#### **System Test**

- Direct implementation of validation boards and testing for HVM screening

- True SLT in high volume for screening DPM level defects in system environment

- Intel's rigorous test methods ensure high quality and reliability of the final part

- Testing for known good individual chiplets, stacked chiplets and final packaged units

## Test Innovation and Cost

- Continuous innovation is needed to meet requirements for sorting next generation chiplets

- Hybrid Bonding bump scaling into single digits and beyond will continue, requiring innovative probe solutions

- Co-packed optics testing is an emerging area → will need some revolutionary ideas for concurrent functional electrical and optical testing

- Test cost will continue to be a major focus

- Tester power density improvement will be needed to minimize additional capital purchase

- Tester and handler parallelism enhancements for multi-unit (site) testing

- Pitch scaling will continue to put pressure on developing cost-effective probe solutions

| Pitch | # Probes | Cost per probe | Probe head cost | Power Delivery | Probe Alignment Margin |

|-------|----------|----------------|-----------------|----------------|------------------------|

|       |          |                |                 |                | Ļ                      |

- Improve test coverage and test time optimization using features such as DFT, BIST

- Right balance between cost of process complexity vs test cost is important

- Application of redistribution layer (RDL) vs continuous pitch scaling

- Singulated die testing with reconstitution vs wafer level testing

- Advanced Packaging Era and the Disaggregated Flow is here to stay in the semiconductor industry

- It is critical to identify Known Good Die (KGD) and catch all defects prior to assembly in advanced packaging

- Intel's unique Test solutions based on HDMT platform and die-level test capability with SDx equipment, ensure KGD

- Intel's HDMT (tester) is available for use by IFS (Intel Foundry) Test Services customers with support from emerging ecosystem

- Cost-effective test innovations are essential to meet emerging product needs

#

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of products, services or technologies needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, services or technologies that are in development and usage may change over time. Product, service and technology performance varies by use, configuration and other factors. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Learn more at <a href="https://www.lntel.com/PerformanceIndex">www.lntel.com/PerformanceIndex</a> and <a href="https://www.lntel.com/PerformanceInd

Reference to research results, including comparisons to products, services or technology performance are estimates and do not imply availability. The products and services described may contain defects or errors which may cause deviation from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings releases, annual report on form 10-K and other SEC filings at <u>www.intc.com</u>.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others. This document contains information on products and technologies in development.