# Digital Lithography Enhances Fine Pitch Probe Cards Performance

Ksenija Varga EV Group

SW/Test | June 3 - 5, 2024

- EV Group: Introduction & Technologies

- Digital Lithography in Fine Pitch Probe Cards Manufacturing

- Methods, Materials and Procedures

- Results & Discussions

- **Conclusions & Outlook**

- Follow–On Work

#### **EV Group | Introduction & Technologies**

Leading supplier of wafer processing equipment for the MEMS, nanotechnology & semiconductors markets.

Founded in 1980 by DI Erich and Aya Maria Thallner. More than 1300 employees worldwide.

Headquarters in Austria, with fully owned subsidiaries in the USA, Japan, South Korea, China, Taiwan & Malaysia.

#### **Digital Lithography | Fine Pitch Probe Cards**

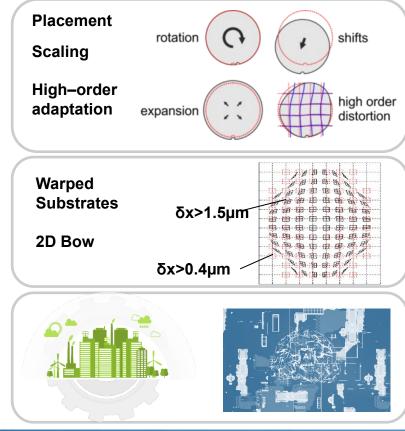

#### PATTERNING REQUIREMENTS

- Several RDLs, small via opening <5 µm, steep via profiles.

- Adaptive lithography with "on–the–fly" distortion compensation.

- Warpage handling in complex packages.

- Economic benefits.

#### MATERIAL REQUIREMENTS

- Dielectric polyimides enabling high-resolution patterning.

- PFAS–Free Formulation, Sustainability.

#### Digital Lithography | Methods, Materials & Processes

- EVG's Maskless Exposure Technology.

- High Resolution Polyimide Dielectric Materials: newly developed, low temperature cure by Fujifilm.

- Substrates: 200mm both, Si and PVD Cu wafers.

- Metrology: CD SEM for top/bottom via measurement & SEM cross–sections.

# EXPOSURE MATRIX DOSE/FOCUS/WAVELENGTH

| PROCESS                        | PARAMETERS                                                                                                                                                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wavelengths<br>[nm]            | 375, 405                                                                                                                                                                                                              |

| DOSE<br>RANGE<br>[mJ/cm²]      | LTC 9320–E76B next gen<br>Si substrate 300–1050<br>Cu substrate 225–975<br>LTC 25000<br>Si and Cu substrates 300–1050                                                                                                 |

| FOCUS<br>RANGE [µm]            | From –14 to +6 above dielectric surface $\rightarrow$ In 2 µm steps                                                                                                                                                   |

| Post<br>Exposure<br>Processing | TARGET FT = 5 $\mu$ m<br>Hard Bake at 100 °C for 60 s<br>Cure at 230 °C for 3h<br>$\rightarrow$ Followed by O <sub>2</sub> –plasma descum to<br>remove residues in contact and bond pads.<br>Target removal of 2000A. |

#### **Digital Lithography | Methods, Materials & Processes**

#### Digital Lithography | Results & Discussion

### $\bigcirc$

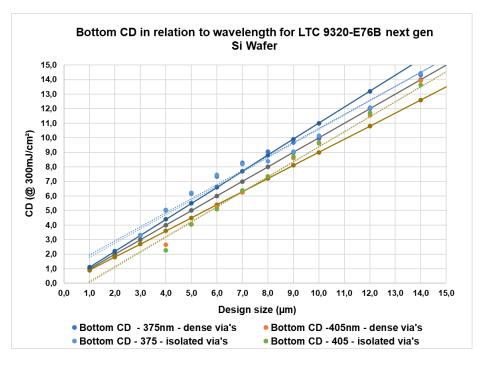

LINEARITY INVESTIGATION at λ≈375nm and 405nm Si Wafers

- Small via size: slight difference in measured bottom CD to digital design size.

- The bottom CD of via exposed at 405 nm is lower than via exposed at 375 nm, for the dense via design.

- Linear interpolations indicate fluctuations and unveil a slight non–linearity of the response.

- The lower resolution limits are affected by the offset in exposure due to over and under– exposure effects.

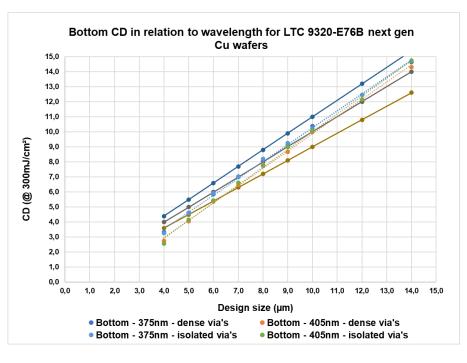

#### LINEARITY INVESTIGATION at λ≈375nm and 405nm Cu Wafers

The advantage of digital systems:

$\rightarrow$ digital corrections & layout compensation processes can be performed more efficiently compared to the corrections required in mask– based systems.

- Real time adaptations of process parameters is allowed.

- Lower resolution on plated Cu:

- $\rightarrow$ due to substrate granularity

$\rightarrow$ leading to poorer pattern definition through light scattering and interaction in the exposure area.

#### Digital Lithography | Results & Discussion

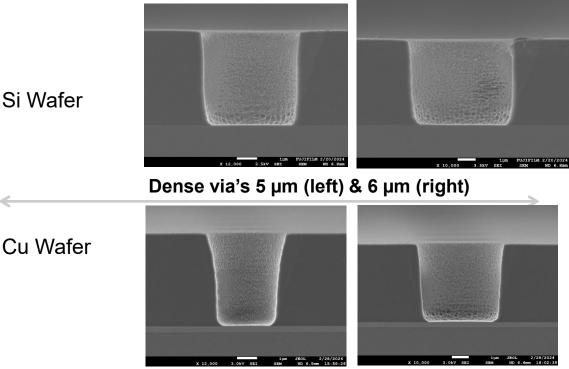

#### PI Dielectric: LTC 9320 E76B next gen INFLUENCE of EXPOSURE at λ≈375nm on VIA PROFILES

#### Isolated via's 4 µm (left) & 5 µm (right).

#### Si wafers

→ Very steep via profiles are resolved for the bottom via CD of 4  $\mu$ m (angle=100.3°) and 5  $\mu$ m (angle=98.5°).

Via size labeling is defined by the exposure equipment's design settings (layout resolution values).

#### Digital Lithography | Results & Discussion

#### PI Dielectric: LTC25000 INFLUENCE of EXPOSURE at λ≈375nm on VIA PROFILES

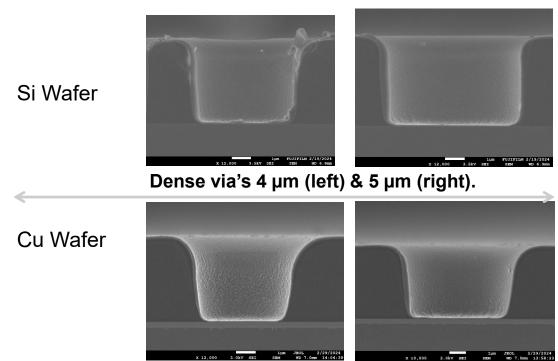

Dense via's 4 µm (left) & 5 µm (right)

- The side wall profiles obtained on patterned PI on the Cu substrates reveal very similar profiles like those obtained on Si substrates.

- The targeted minimal footing was achieved with the optimized digital processing parameters

- $\rightarrow$  obtained from the test exposure matrix.

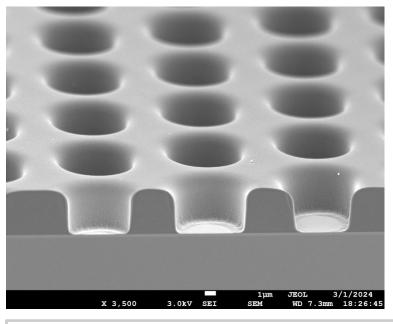

TOP TILTED VIEW of SEM CROSS– SECTION IMAGE of DENSE VIA

$\rightarrow$  EXPOSED at 375nm for high resolution PI on Cu–wafer.

$\rightarrow$  Steep via opening accomplishes homogenous metallization in subsequent integration processes.

PI Dielectric LTC 9320-E76B next gen

BOTTOM VIA OPENING = 5 µm

$\bigcirc$

The objective of developing **lithographic patterning for use in probe cards** has been successfully achieved.  $\overline{\mathbf{r}}$

Both next gen polyimide dielectrics, LTC versions developed by Fujifilm demonstrated **<5 µm via diameter** capability.

**Steep via profiles** of PI facilitate improvement of integration processes and achievement of high electrical properties.

Versatility of **mix–and–match exposure** wavelengths allows for the exploration of novel materials processing techniques.

EVG's digital lithography equipment, LITHOSCALE<sup>®</sup>, is designed to facilitate rapid R&D prototyping & expeditious transition from to HVM.  $\overline{\mathbf{a}}$

LITHOSCALE<sup>®</sup> plays significant role in the **digital transformation of lithography** in semiconductor testing equipment.

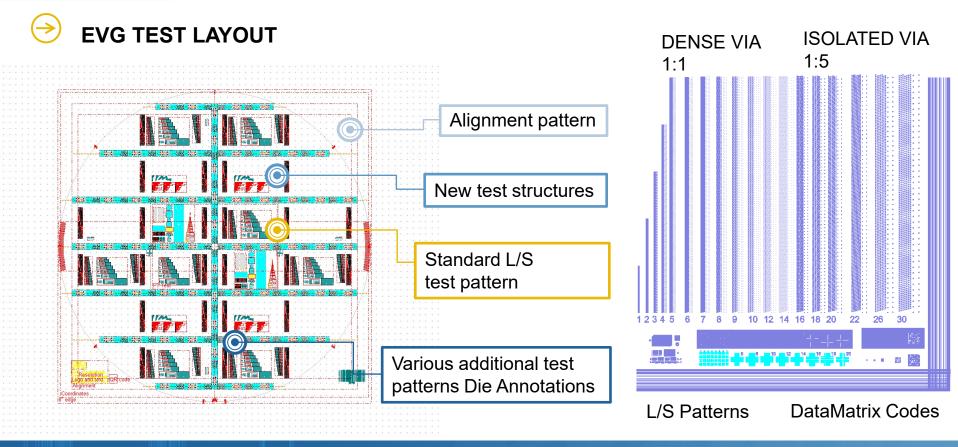

#### Digital Lithography | Follow–On Work

- Traceability in Semiconductors.

- Automotive & Security Applications.

- Enabled by Die Annotation

Software Feature on LITHOSCALE<sup>®</sup>.

- Proven readable DataMatrix

Codes in dimensions 50×50 µm squares with specialty RGB resists.

## **Thanks for your Attention!**

**Contact us with any questions ...**

Ksenija Varga Business Development Manager EV Group E: k.varga@evgroup.com

Stefan Vanclooster Global Business Director Polyimides Fujifilm Electronic Materials E: stefan.vanclooster@fujifilm.com